課題番号 : 2023B-E17

利用課題名(日本語): 高性能 MOS 型パワーデバイス実現に向けたヘテロ界面評価とその制御技術の開発

Program Title (English) : Characterization and control of insulator/semiconductor and metal/semiconductor interfaces

for power MOS devices

利用者名(日本語) : 渡部平司, 小林拓真, 野崎幹人, 溝端秀聡

Username (English) : H. Watanabe, T. Kobayashi, M. Nozaki, H. Mizobata

所属名(日本語) : 大阪大学大学院工学研究科

キーワード: GaN, SiC, XPS

## 1. 概要(Summary)目的・用途・実施内容

SiC や GaN はその優れた物性から高性能なパワーデバイス材料として期待されているが、その実現には欠陥の少ない高品質な MOS 構造の実現が求められる。本研究では放射光 XPS 測定により SiC 及び GaN 上に形成した絶縁膜/半導体界面の評価を目指した。

## 2. 実験(目的,方法) (Experimental)

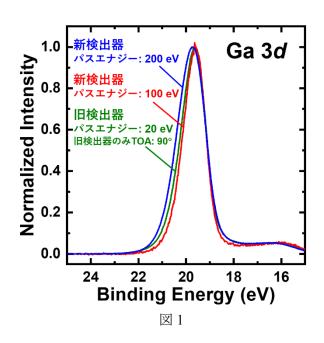

2023 年度に検出器系が更新された SPring-8 BL23SU 表面化学実験ステーションにて薄膜 SiO<sub>2</sub>/GaN 試料及び SiO<sub>2</sub>/SiC 試料の MOS 界面構造の評価を試みた。本報告 書では図 1 に GaN 基板表面の Ga 3d スペクトルについ てのみ報告する。光電子脱出角度は装置標準の 63°とし、X 線エネルギーは 1253.6 eV で測定を行った。

## 3. 結果と考察(Results and Discussion)

新検出器系では S/N と分解能を両立した信号が得られていないことから今期の全 2 回の実験では測定条件の最適化を試みた。2回目の実験時に検出器のアパーチャー等を変更し S/N の改善が見られたが、例えば価電子帯スペクトル等から精度良く絶縁膜/半導体界面のバンドオフセットを求めるためには更なる S/N の改善が必要である。ビームタイム終了が近づく頃、パスエナジーの変更(100 eV → 200 eV)と合わせて、マルチチャンネルプレートや検出器側のスリット幅の設定を調整し、旧検出器系に近いレベルのS/N が得られたが、ピークの幅広化が見られており(図 1)、強度と分解能の両立を目指した更なる最適化が求められる。

## 4. その他・特記事項 (Others)

本研究の一部は、文部科学省革新的パワーエレクトロニクス創出基盤技術研究開発事業(JPJ009777)および JSPS 科研費(23K13367)の助成を受けた。